# Extending a Tableau-based SAT Procedure with Techniques from CNF-based SAT

# DIPLOMARBEIT

zur Erlangung des akademischen Grades

## **Diplom-Ingenieur**

im Rahmen des Studiums

## **Computational Intelligence**

ausgeführt von

## Leopold Carl Robert Haller

Matrikelnummer 0355898

an der Fakultät für Informatik der Technischen Universität Wien

Betreuung: Betreuer: Ao. Univ.-Prof. Dr. Uwe Egly

Wien, 1.12.2008

(Unterschrift Verfasser)

(Unterschrift Betreuer)

#### Abstract

Das propositionale Erfüllbarkeitsproblem (SAT) ist ein klassisches Entscheidungsproblem der theoretischen Informatik. Es war das erste Entscheidungsproblem, für das NP-Vollständigkeit bewiesen wurde, und Implementierungen von Lösungsalgorithmen für SAT-Instanzen werden seit den frühen 1960ern erforscht. Ein spezieller Fokus liegt hier historisch auf der Betrachtung von SAT-Problemen, die in konjunktiver Normalform (KNF) gegeben sind.

In den letzten führzehn Jahren hat sich die Effizienz solcher KNF-basierter Lösungsalgorithmen enorm verbessert. Programme, die das Erfüllbarkeitsproblem lösen (sogenannte SAT-Solver), finden heute vielfältige Anwendung in Industrie und Forschung, etwa in Soft- und Hardwareverifikation und in Logik-basierter Planung.

In vielen praktischen Anwendungsgebieten von SAT-Solvern sind die Eingabedaten als strukturierte Formeln oder Schaltkreise gegeben. Um solche Instanzen mit KNFbasierten Solvern zu lösen muss zuerst ein Übersetzungsschritt durchgeführt werden. Dabei geht die ursprüngliche Strukturinformation der Formel verloren, wodurch der Einsatz strukturbasierter Heuristiken zum Beschleunigen des Lösungsprozesses unmöglich wird.

In dieser Arbeit wird eine Erweiterung des BC-Tableaukalküls zur Feststellung der Erfüllbarkeit von beschränkten kombinatorischen Schaltkreisen vorgestellt. Eine kurze Einführung in propositionale Logik und das Erfüllbarkeitsproblem (SAT) wird gegeben, und es wird der klassische Davis-Logemann-Loveland-Algorithmus (DLL) zur Lösung von SAT-Instanzen in konjunktiver Normalform präsentiert. Es wird aufgezeigt, wie moderne KNF-Solver das grundlegende DLL-Schema um nicht-chronologisches Backtracking und Lernen erweitern. Techniken werden beschrieben, mithilfe derer SAT-Solver in der Lage sind praktisch relevante Probleme in Industrie und Forschung zu lösen, und es werden Ansätze diskutiert um das Lösen des SAT-Problems in Schaltkreisinstanzen zu beschleunigen.

Es wird gezeigt, dass eine Implementierung des BC-Tableaus als generalisierte DLL-Prozedur gesehen werden kann, und es wird dargestellt, wie sich Techniken aus dem Bereich des KNF-basierten SAT-Solving in das BC-Tableau integrieren lassen. Ein Prototyp einer solchen erweiterten Tableauprozedur wurde entwickelt und seine Effektivität im Vergleich zu bestehenden SAT-Solvern evaluiert. Es zeigt sich, dass die Erweiterung des BC.Tableaus die durchschnittliche Geschwindigkeit in Benchmarks wesentlich verbessert, und dass das erweiterte BC-Tableau als Grundlage für Schaltkreis-basierte SAT-Solver durchaus mit modernen KNF-basierten Implementierungen Schritt halten kann.

#### Abstract

The propositional satisfiability problem (SAT) is one of the central decision problems in theoretical computer science. It was the first decision problem that was proven to be NP complete, and the study of implementations of decision procedures for SAT date back to the early 1960s. In the area of satisfiability research, work on SAT instances given in conjunctive normal form (CNF) has been a major focus of research.

In the last 15 years, the efficacy of CNF-based SAT algorithms, i.e., algorithms for instances of propositional formulas in conjunctive normal form (CNF), has increased significantly. Today, SAT solvers are employed in a number of applications in industry and science such as software and hardware verification or logic-based planning.

In many application areas of SAT, the instances are originally given as structured formulas or circuit instances. Using a CNF-based SAT solver on such instances requires a translation step from the original formula to CNF. The result lacks the structural information of the original instance, which could have been used heuristically to speed up the solving process.

In this thesis, we present an extension of the BC tableau calculus for determining satisfiability of constrained Boolean circuits. We give a short introduction to propositional logic and the SAT problem, and we present classical algorithms for solving SAT such as the Davis-Putnam (DP) procedure and the Davis-Logemann-Loveland (DLL) procedure. Modern extensions to the basic DLL framework, such as non-chronological backtracking and clause learning, are discussed, which reduce solving time on industrial instances considerably. We also present some approaches for solving the SAT problem in circuits.

We show that a BC-tableau-based SAT algorithm can be seen as a generalization of the basic DLL procedure and how techniques from CNF-based SAT can be integrated into such a tableau procedure. We present a prototypical implementation of these ideas and evaluate it using a set of benchmark instances. The extensions increase the efficiency of the basic BC tableau considerably, and the framework of our extended BC-tableau solver is shown to be competitive with state-of-the-art CNF-based solving procedures.

# Contents

| 1        | Introduction                             |         |                                                               |           |  |  |  |  |

|----------|------------------------------------------|---------|---------------------------------------------------------------|-----------|--|--|--|--|

| <b>2</b> | The Propositional Satisfiability Problem |         |                                                               |           |  |  |  |  |

|          | 2.1                                      | Basic   | Definitions and Terminology                                   | 5         |  |  |  |  |

|          |                                          | 2.1.1   | Propositional Logic                                           | 5         |  |  |  |  |

|          |                                          | 2.1.2   | Boolean Circuits                                              | 8         |  |  |  |  |

|          | 2.2                                      | The P   | ropositional Satisfiability Problem                           | 10        |  |  |  |  |

|          | 2.3                                      | Basic   | Algorithms for the SAT-Problem                                | 11        |  |  |  |  |

|          |                                          | 2.3.1   | The Davis-Putnam Algorithm                                    | 13        |  |  |  |  |

|          |                                          | 2.3.2   | The Davis-Logemann-Loveland Algorithm                         | 15        |  |  |  |  |

|          | 2.4                                      | Practi  | cal Applications of SAT-Solvers                               | 17        |  |  |  |  |

|          |                                          | 2.4.1   | Bounded Model Checking                                        | 17        |  |  |  |  |

|          |                                          | 2.4.2   | Automatic Test Pattern Generation                             | 18        |  |  |  |  |

| 3        | Imp                                      | orovem  | ents Over The Standard DLL Framework                          | <b>21</b> |  |  |  |  |

|          | 3.1                                      | The D   | LL Algorithm Revisited                                        | 22        |  |  |  |  |

|          | 3.2                                      | Clause  | e Learning and Non-Chronological Backtracking                 | 23        |  |  |  |  |

|          |                                          | 3.2.1   | Clause Learning                                               | 23        |  |  |  |  |

|          |                                          | 3.2.2   | Non-Chronological Backtracking                                | 26        |  |  |  |  |

|          |                                          | 3.2.3   | DLL with Clause Learning and Non-Chronological Backtracking . | 27        |  |  |  |  |

|          |                                          | 3.2.4   | Backtracking to the Second-Highest Decision Level             | 27        |  |  |  |  |

|          |                                          | 3.2.5   | Clause-Database Management                                    | 32        |  |  |  |  |

|          | 3.3                                      | Strate  | gies for Clause Learning                                      | 32        |  |  |  |  |

|          |                                          | 3.3.1   | Unique Implication Points (UIP)                               | 33        |  |  |  |  |

|          |                                          | 3.3.2   | Choosing a Cut for a Learned Clause                           | 35        |  |  |  |  |

|          | 3.4                                      | Efficie | nt Datastructures for BCP                                     | 36        |  |  |  |  |

|          |                                          | 3.4.1   | Counter-Based Approaches                                      | 36        |  |  |  |  |

|          |                                          | 3.4.2   | Head/Tail Lists and Literal Watching                          | 37        |  |  |  |  |

|          |                                          | 3.4.3   | Special Handling of Small Clauses                             | 39        |  |  |  |  |

|          | 3.5                                      | Variab  | ble Selection Heuristics                                      | 41        |  |  |  |  |

|          |                                          | 3.5.1   | Early Heuristics                                              | 41        |  |  |  |  |

|          |                                          | 3.5.2   | Second-Order Heuristics                                       | 42        |  |  |  |  |

|          | 3.6                                      | Restar  | ting and Randomizing the Search                               | 43        |  |  |  |  |

|          | 3.7                                                  | Simpli<br>3.7.1<br>3.7.2         | fying CNF formulas44Preprocessing SAT Instances46On-the-fly Clause-Database Simplifications48                                                    |  |  |  |  |  |  |  |

|----------|------------------------------------------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 4        | Solv                                                 | $\operatorname{ving} \mathbf{S}$ | AT in Circuits 50                                                                                                                                |  |  |  |  |  |  |  |

|          | 4.1                                                  | 0                                | nt Circuit-to-CNF Translations                                                                                                                   |  |  |  |  |  |  |  |

|          |                                                      | 4.1.1                            | The Tseitin Transformation                                                                                                                       |  |  |  |  |  |  |  |

|          |                                                      | 4.1.2                            | Producing Short Clause-Forms                                                                                                                     |  |  |  |  |  |  |  |

|          |                                                      | 4.1.3                            | Enriching CNF with Deduction Shortcuts                                                                                                           |  |  |  |  |  |  |  |

|          | 4.2                                                  | Combi                            | ning Circuit-SAT and CNF-SAT                                                                                                                     |  |  |  |  |  |  |  |

|          |                                                      | 4.2.1                            | Introducing Circuit Information into CNF-SAT                                                                                                     |  |  |  |  |  |  |  |

|          |                                                      | 4.2.2                            | Circuit-SAT with Clause Learning                                                                                                                 |  |  |  |  |  |  |  |

|          | 4.3                                                  | Circuit                          | t-based Approaches                                                                                                                               |  |  |  |  |  |  |  |

| <b>5</b> | Implementing an Extended Tableau-Based SAT Solver 66 |                                  |                                                                                                                                                  |  |  |  |  |  |  |  |

|          | 5.1                                                  | Tablea                           | u-Based SAT Solving                                                                                                                              |  |  |  |  |  |  |  |

|          |                                                      | 5.1.1                            | The BC Tableau                                                                                                                                   |  |  |  |  |  |  |  |

|          |                                                      | 5.1.2                            | Circuit Reduction                                                                                                                                |  |  |  |  |  |  |  |

|          |                                                      | 5.1.3                            | Tableau-Based SAT as Generalized DLL    75                                                                                                       |  |  |  |  |  |  |  |

|          |                                                      | 5.1.4                            | BC with Learning and Non-Chronological Backtracking 76                                                                                           |  |  |  |  |  |  |  |

|          |                                                      | 5.1.5                            | Datastructures for Deduction                                                                                                                     |  |  |  |  |  |  |  |

|          | 5.2                                                  | Impler                           | nenting an Enhanced Tableau-Based Solver                                                                                                         |  |  |  |  |  |  |  |

|          |                                                      | 5.2.1                            | Basic Datastructures                                                                                                                             |  |  |  |  |  |  |  |

|          |                                                      | 5.2.2                            | Deduction $\ldots \ldots \ldots$ |  |  |  |  |  |  |  |

|          |                                                      | 5.2.3                            | Conflict Analysis, Learning and Backjumping                                                                                                      |  |  |  |  |  |  |  |

|          |                                                      | 5.2.4                            | Circuit Reduction                                                                                                                                |  |  |  |  |  |  |  |

|          |                                                      | 5.2.5                            | One-Step Lookahead                                                                                                                               |  |  |  |  |  |  |  |

|          |                                                      | 5.2.6                            | Decision Variable Selection                                                                                                                      |  |  |  |  |  |  |  |

|          |                                                      | 5.2.7                            | Restarts                                                                                                                                         |  |  |  |  |  |  |  |

| 6        | $\mathbf{Res}$                                       | ults                             | 90                                                                                                                                               |  |  |  |  |  |  |  |

| Ū        | 6.1                                                  | Compa                            | aring Decision Heuristics                                                                                                                        |  |  |  |  |  |  |  |

|          | 6.2                                                  | _                                | ting Lookahead                                                                                                                                   |  |  |  |  |  |  |  |

|          | 6.3                                                  |                                  | ting Schemes                                                                                                                                     |  |  |  |  |  |  |  |

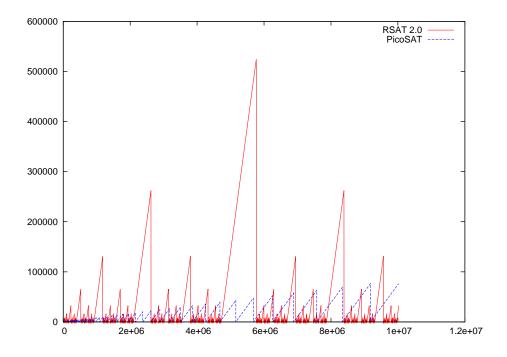

|          | 6.4                                                  |                                  | aring BattleAx <sup>3</sup> with other SAT Solvers $\ldots \ldots \ldots \ldots \ldots \ldots \ldots 96$                                         |  |  |  |  |  |  |  |

| 7        | Cor                                                  | clusio                           | n 100                                                                                                                                            |  |  |  |  |  |  |  |

| •        | 7.1                                                  |                                  | ting Results                                                                                                                                     |  |  |  |  |  |  |  |

|          | 7.2                                                  |                                  | Questions and Research Opportunities                                                                                                             |  |  |  |  |  |  |  |

|          | 7.3                                                  | -                                | Iding Remarks                                                                                                                                    |  |  |  |  |  |  |  |

# Chapter 1 Introduction

The propositional satisfiability problem (SAT) is the problem of deciding for a propositional formula whether there is a variable assignment under which the formula evaluates to true. In computer science, the SAT problem has a history as a problem of both theoretical and practical interest. Early implementations of solvers, such as the Davis-Logemann-Loveland procedure, date back to the early 1960s [12; 13]. The SAT problem was also the first decision problem proved to be NP complete in the early 1970s [10].

More recently, work on the propositional satisfiability problem has shifted somewhat towards the practical side. SAT solvers have been applied to a number of real-world problems, including hardware and software verification and logic-based planning. At the same time, building efficient solvers for the propositional satisfiability problem has become a major focus of research.

An enormouse effort so far has concentrated on extending the basic Davis-Logemann-Loveland procedure which works on satisfiability instances given in conjunctive normal form (CNF), but, increasingly, this work is being extended to non-clausal SAT instances. Intuitively, it seems likely that the added structural information can be used to speed up the solving process, but work on non-clausal SAT still has a long way to go. At this time, state-of-the-art CNF-based SAT solvers coupled with translation front-ends for non-clausal instances still outperform dedicated non-clausal solvers [45].

One of the reasons for this is that a lot of effort has been invested into engineering efficient CNF-based solvers. The structurally simple CNF format lends itself very well to fast and cache-efficient low-level implementation techniques and can be naturally extended with techniques such as clause-learning and non-chronological backtracking. Circuit-based solvers have yet to match this level of engineering.

In this thesis, we will give a brief introduction to propositional logic, the propositional satisfiability problem, and its applications. We will explain some techniques from the area of CNF-based SAT which have proven to increase efficiency in practical instances, and we will show some of the attempts that have been made to solve the SAT problem directly in structured problem instances. Finally, we will present the BC tableau, a tableau calculus for solving the SAT problem in Boolean circuits, and we will discuss how a BC tableau procedure can be extended in a generalized DLL framework with

many of the techniques used in CNF-based SAT, such as non-chronological backtracking, learning, and restarts. We present  $BattleAx^3$  ("BattleAx Cube" being an anagram of "BC Tableau Ext."), a prototype of such an extended BC-based procedure, describe its implementation, and compare it both to the original BC procedure and to MiniSAT, an efficient CNF-based solver.

The structure of this thesis is as follows. Chapter 2 introduces basic terminology and notation and gives a brief introduction to propositional logic. It also presents the original Davis-Putnam (DP) [12] and Davis-Logemann-Loveland (DLL) [13] procedures that form the basics of modern solvers. Chapter 3 gives an overview of modern CNF-based SAT solving. We explain extensions to the basic DLL framework such as non-chronological backtracking and learning, efficient implementation techniques, and common solving heuristics. In Chapter 4, the area of solving SAT for circuit instances is discussed. This includes a description of circuit-to-CNF translation techniques, circuit extensions for CNF-based SAT solvers, and dedicated circuit-based solvers. Chapter 5 presents the BC tableau and shows how a BC-based solver can be implemented in a generalized DLL framework and extended with many of the techniques found in CNF-based SAT. It also gives a detailed description of the prototypical implementation BattleAx<sup>3</sup>. Chapter 6 provides benchmarking results for BattleAx<sup>3</sup>, compares a number of different solving strategies, and compares it with the original BC procedure and the CNF-based MiniSAT SAT solver. Finally, Chapter 7 provides a conclusion.

# Chapter 2

# The Propositional Satisfiability Problem

The propositional satisfiability problem is a central problem in computer science from a theoretical as well as from a practical point of view. It has historical importance as the first problem that was proven to be NP-complete [10], and its analysis and the development of satisfiability decision procedures have spawned a vast array of literature.

One of the main reasons for the high interest in the satisfiability problem is that implementations of satisfiability decision procedures, so-called SAT solvers, have a wide range of possible applications, many of them industrial rather than academic in nature. Advances in SAT-solving from the last fifteen years have made it possible to go beyond toy instances and solve propositional encodings of real-world problems from various domains, such as logic-based planning, automated test pattern generation, and software and hardware verification.

This chapter will serve as a short introduction to propositional logic and the propositional SAT problem. The DP algorithm and its successor, the DLL algorithm, will be described, the latter being the algorithmic framework that still forms the basis of most modern SAT solvers.

### 2.1 Basic Definitions and Terminology

The work in this thesis uses two closely related notions to describe problem instances of satisfiability, propositional logic and Boolean circuits. In this section, we introduce basic terminology and notation and formally characterize both of them.

#### 2.1.1 Propositional Logic

*Propositional logic* (also called propositional calculus, sentential logic, or combinatorial logic) is a branch of mathematical logic that deals with the analysis of well-formed logical formulas built up from propositional atoms and logical connectives.

First, we introduce the syntax of propositional logic by giving an inductive definition of the set  $\mathcal{F}$  of propositional formulas.

**Definition 1.** Let  $\mathcal{B}$  be a countable set of Boolean variables. Then the set  $\mathcal{F}$  of all well-formed propositional formulas is defined inductively as follows.

- (i)  $\mathcal{B} \cup \{\top, \bot\} \subset \mathcal{F}$ .

- (*ii*) If  $\phi \in \mathcal{F}$ , then  $(\neg \phi) \in \mathcal{F}$ .

- (iii) If  $\phi, \psi \in \mathcal{F}$ , then  $(\phi \circ \psi) \in \mathcal{F}$  for  $\circ \in \{\land (conjunction), \lor (disjunction), \Rightarrow (implication), \Leftrightarrow (equivalence)\}.$

For easier readability, brackets may be omitted. In this case, we define the order of binding strength (from strongest to weakest) to be  $\neg, \land, \lor, \Rightarrow, \Leftrightarrow$ .

A formula  $v \in \mathcal{B}$  is called a *propositional atom*. An atom or a negated atom is called a *literal*. Such a literal is said to be in positive or negative phase depending on whether its variable is negated. An unnegated variable is said to be in *positive phase*, while a negated variable is said to be in *negative phase*. The opposite phase literal to a literal lis referred to as  $\overline{l}$ . A disjunction of literals is called a *clause*.

**Definition 2.** Let  $\mathcal{V} = \{\mathbf{T}, \mathbf{F}\}$  be the set of Boolean values. A function  $f : \mathcal{V}^n \mapsto \mathcal{V}$  is called a Boolean function of arity n.

Atoms represent simple statements which can assume the Boolean values true  $(\mathbf{T})$  or false  $(\mathbf{F})$  when modeling some arbitrary domain with propositional logic. Atoms may represent any such proposition, such as "it is raining" or "the value of variable x is greater than zero". Non-atomic formulas describe compound statements whose truth value is related to the component truth values by a Boolean formula. A statement

"it is raining"  $\Rightarrow$  "Anne will stay at home"

for example, is false only if it is raining and Anne leaves her home and true otherwise. This relationship does not depend on the semantic contents of the propositions that are associated with the atoms, but only on their truth values. In order to be able to determine the truth value of such arbitrary statements mechanically, we need to introduce the formal semantics of propositional logic. The first step is to introduce a formal device that assigns truth values to atomic propositions.

**Definition 3.** For a set of Boolean variables  $\mathcal{P}$ , a (possibly partial) function  $I : \mathcal{P} \mapsto \mathcal{V}$  is called an interpretation.

We will call a function I interpretation of a formula  $\phi$  if I is an interpretation of the Boolean variables occurring in  $\phi$ . If I is a partial function, we refer to it as a partial interpretation. Interpretations will also be referred to as variable assignments. An interpretation I' is an extension of an interpretation I, or more concisely,  $I \subseteq I'$ , iff

for any x, if I(x) is defined, then I(x) = I'(x)

Since we want to be able to evaluate the truth values of arbitrary formulas, we extend I to formulas in the following way.

**Definition 4.** For a given interpretation I', let  $I : \mathcal{F} \mapsto \mathcal{V}$  be its extension to formulas, defined in the following way:

- (i)  $I(\top) = \mathbf{T}$

- (*ii*)  $I(\perp) = \mathbf{F}$

- (iii) I(v) = I'(v) iff  $v \in \mathcal{B}$

- (*iv*)  $I(\neg \phi) = \mathbf{T}$  iff  $I(\phi) = \mathbf{F}$

- (v)  $I(\phi \wedge \psi) = \mathbf{T}$  iff  $I(\phi) = I(\psi) = \mathbf{T}$

- (vi)  $I(\phi \lor \psi) = \mathbf{T}$  iff  $I(\phi) = 1$  or  $I(\psi) = \mathbf{T}$

- (vii)  $I(\phi \Rightarrow \psi) = \mathbf{T}$  iff  $I(\phi) = \mathbf{F}$  or  $I(\psi) = \mathbf{T}$

- (viii)  $I(\phi \Leftrightarrow \psi) = \mathbf{T}$  iff  $I(\phi) = I(\psi) = \mathbf{T}$  or  $I(\phi) = I(\psi) = \mathbf{F}$

For easier readability, no distinction will be made between interpretations and their extensions to formulas. Furthermore, if it is clear from the context which interpretation I is being referred to, we will use the notation v := X to indicate that I(v) = X. We now introduce some further notions that will be needed later on.

**Definition 5.** An interpretation I of a propositional formula  $\phi$  is called a model of  $\phi$ iff  $I(\phi) = \mathbf{T}$ . The set of all models of  $\phi$  is  $Mod(\phi)$ .

For example, given the formula  $a \Rightarrow b$ , both  $\{a \mapsto \mathbf{F}, b \mapsto \mathbf{T}\}$  and  $\{a \mapsto \mathbf{T}, b \mapsto \mathbf{F}\}$  are interpretations, but only the former is a model. A number of equivalent ways will be used to express the model attribute of an interpretation.

**Remark.** Given a propositional formula  $\phi$ , the following notions are equivalent:

- (i) I is a model of  $\phi$

- (*ii*)  $I \models \phi$

- (iii) I satisfies  $\phi$

- (*iv*)  $I \in Mod(\phi)$

**Definition 6.** A formula  $\phi$  is satisfiable iff  $Mod(\phi) \neq \emptyset$ , otherwise it is unsatisfiable.

**Definition 7.** A formula  $\phi$  is valid iff for every interpretation I, it holds that  $I \models \phi$ .

We now define the subformula relations on formulas.

**Definition 8.** The formula  $\phi$  is an immediate subformula of  $\psi$  iff one of the following conditions holds

- (i)  $\psi = \neg \phi$ ,

- (*ii*)  $\psi = (\phi \circ \omega) \text{ or } \psi = (\omega \circ \phi) \text{ for } \circ \in \{\land, \lor, \Rightarrow, \Leftrightarrow\}.$

The formula  $\phi$  is a subformula of  $\psi$  iff  $(\phi, \psi)$  is in the transitive closure of the immediate subformula relation.

#### 2.1.2 Boolean Circuits

Boolean circuits are mathematical models of digital combinatorial circuits, i.e., digital circuits where no outputs are fed back into the circuit as inputs. They are closely related to propositional formulas. Translation strategies will be described in Chapter 4.

The following characterization of Boolean circuits is mostly taken from Drechsler, Juntilla, and Niemelä [14].

**Definition 9.** A Boolean circuit C is a pair  $(\mathcal{G}, \mathcal{E})$ , where

(i)  $\mathcal{G}$  is a non-empty finite set of gates

(ii)  $\mathcal{E}$  is a set of equations where

- each equation is of the form  $g := f_g(g_1, \ldots, g_n)$ , where  $g, g_1, \ldots, g_n \in \mathcal{G}$  and  $f_g : \mathcal{V}^n \mapsto \mathcal{V}$  is a Boolean function,

- each gate  $g \in G$  appears at most once on the left-hand side in the equations in  $\mathcal{E}$ , and

- the dependency graph, graph(C) = (G, {(g,g') | g := f(...,g',...)}) is acyclic, i.e., no gate is defined recursively.

A gate that does not occur on the left hand side of any equation in  $\mathcal{E}$  is called a *primary input gate*, a set that does not occur on the right hand side of any equation is called a *primary output gate*. The set of primary input and primary output gates of a circuit  $\mathcal{C}$  is designated by  $input(\mathcal{C})$  and  $output(\mathcal{C})$  respectively.

For any gates g and g', if g' appears on the right-hand side of g's equation, we call g a parent of g' and g' a child of g. The ancestor and descendant relation between gates are defined intuitively as the transitive closures of the parent and child relation respectively.

A subcircuit is a part of a larger circuit,

**Definition 10.** Given two Boolean circuits  $C = (\mathcal{G}, \mathcal{E})$  and  $C' = (\mathcal{G}', \mathcal{E}')$ , we call C' a subcircuit of C iff

- $\mathcal{E}' \subseteq \mathcal{E}$  and

- $\mathcal{G}' = \{ v, c_1, \dots, c_n \mid v := f_v(c_1, \dots, c_n) \in \mathcal{E}' \}$

In this thesis, only certain classes of Boolean functions will be associated with gates in gate equations. These include

- the constant functions  $true() = \mathbf{T}$  and  $false() = \mathbf{F}$ ,

- $not: \mathcal{V} \mapsto \mathcal{V}, not(\mathbf{T}) = \mathbf{F}, not(\mathbf{F}) = \mathbf{T}$

- and:  $\mathcal{V}^n \mapsto \mathcal{V}$ ,  $and(v_1, \ldots, v_n) = \mathbf{T}$  iff all  $v_1$  to  $v_n$  are  $\mathbf{T}$ .

- or:  $\mathcal{V}^n \mapsto \mathcal{V}$ ,  $or(v_1, \ldots, v_n) = \mathbf{T}$  iff at least one of  $v_1$  to  $v_n$  is  $\mathbf{T}$ .

- *ite*:  $\mathcal{V}^3 \mapsto \mathcal{V}$ , this is the if-then-else construct. The value of  $ite(v_c, v_1, v_2)$  is the value of  $v_1$  if  $v_c = \mathbf{T}$  and the value of  $v_2$  if  $v_c = \mathbf{F}$ .

- odd:  $\mathcal{V}^n \mapsto \mathcal{V}$ ,  $odd(v_1, \ldots, v_n) = \mathbf{T}$  iff the number of input values  $v_c$  with  $v_c = \mathbf{T}$  is odd.

- even:  $\mathcal{V}^n \mapsto \mathcal{V}$ ,  $even(v_1, \ldots, v_n) = \mathbf{T}$  iff the number input values  $v_c$  with  $v_c = \mathbf{T}$  is even.

- equiv:  $\mathcal{V}^n \mapsto \mathcal{V}$ , equiv $(v_1, \ldots, v_n) = \mathbf{T}$  iff  $v_1 = \cdots = v_n$ .

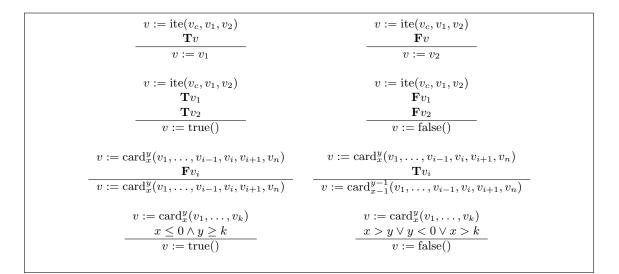

- $card_x^y : \mathcal{V}^n \mapsto \mathcal{V}$ , this is the cardinality gate,  $card_x^y(v_1, \ldots, v_n) = \mathbf{T}$  iff at least x and at most y input values are  $\mathbf{T}$ .

We call a (possibly partial) function  $\tau : \mathcal{G} \mapsto \mathcal{B}$  a truth assignment of  $\mathcal{C}$ . A partial truth assignment is a truth assignment whose function is partial. If for a gate g,  $\tau(g)$  is defined, we say that g is *assigned*. A truth assignment in which all gates are assigned is a *total* truth assignment.

A truth assignment  $\tau'$  is an extension of an assignment  $\tau$  iff  $\tau(g) = \tau'(g)$  for all gates  $g \in \mathcal{G}$  that are assigned in  $\tau$ , i.e.,  $\tau \subseteq \tau'$ .

A total truth assignment  $\tau$  is consistent in a circuit C iff, for each gate  $g \in \mathcal{G}$  with associated Boolean function  $f_g(g_1, \ldots, g_n)$ , it holds that  $f_g(\tau(g_1), \ldots, \tau(g_n)) = \tau(g)$ . We call a gate g justified in a truth assignment  $\tau$  if, for any satisfying truth assignment  $\tau'$  where for each of g's children  $g_c \tau'(g_c) = \tau(g_c)$  (if  $\tau(g_c)$  is defined), it holds that  $\tau(g) = \tau'(g)$ . Intuitively, a gate is justified in  $\tau$  if its output is fully explained by the values of its children that are set in  $\tau$ . An AND-gate with value  $\mathbf{F}$  in  $\tau$ , for example, is justified, if one of its children also has value  $\mathbf{F}$  in  $\tau$ . No matter what values the other children will take on, the gate output will not change.

It is easy to see that a given circuit C has  $2^{|input(\mathcal{C})|}$  consistent truth assignments, that is, there is one distinct satisfying truth assignment for each truth assignment on the input gates. Such an assignment can be found by determining the values of all non-input gates by applying the corresponding gate function in a bottom-up fashion.

A constrained circuit is a pair  $(\mathcal{C}, \tau)$  where  $\mathcal{C}$  is a Boolean circuit and  $\tau$  is a non-empty (possibly partial) truth assignment. A constrained circuit is called satisfiable, iff there is an extension  $\tau'$  of  $\tau$  that is consistent in  $\mathcal{C}$ .

The behavior of a Boolean circuit can be modeled by a propositional formula. The Boolean function for the value of a given output gate can be determined by starting with its associated Boolean function and replacing each gate occurrence with its own function in turn, until no more replacements are possible. We will denote this exhaustive replacement process of a formula f with expand(f). A full propositional modeling of a circuit C's behavior is then given by

$$\bigwedge_{o \in output(\mathcal{C})} o \Leftrightarrow expand(f_o)$$

A serious drawback of this translation is that the formula size may increase exponentially when transforming it into a normal form. More sophisticated translation strategies

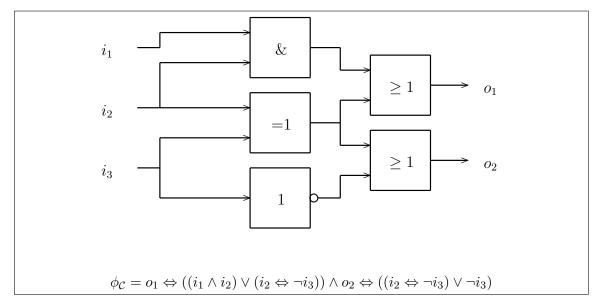

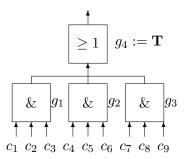

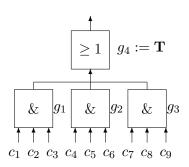

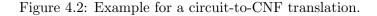

Figure 2.1: Example of a Boolean circuit and a corresponding propositional formula.

which circumvent this problem will be described in detail in Chapter 4. An example of a Boolean circuit and a corresponding propositional formula is shown in Figure 2.1.

### 2.2 The Propositional Satisfiability Problem

The propositional satisfiability problem (SAT) is a central decision problem in computer science, and it can be stated in its general form in the following way:

**Definition 11.** For a given propositional formula  $\phi$ , the Boolean satisfiability problem *(SAT)* is to decide whether  $\phi$  is satisfiable, i.e., whether there is an interpretation I of  $\phi$  so that  $I \models \phi$ .

The propositional satisfiability problem was the first decision problem proven to be NP-complete in [10], that is, it can be solved by a non-deterministic Turing machine in polynomial time, and every other member of NP can be cast into an instance of SAT by a polynomial-time transformation algorithm. All known algorithms that decide the Boolean satisfiability problem have an exponential worst-case time complexity.

Much work on the SAT-problem has been done on propositional formulas in normal forms, the most prominent being *conjunctive normal form* (CNF). A CNF formula is a conjunction of clauses, it can be pictured as a two-level circuit where multiple OR-gates feed into one AND gate. We can easily transform any given formula  $\phi$  into an equivalent CNF-formula by exhaustively replacing subformulas of  $\phi$  with the substitutions from Table 2.1.

The problem with this kind of transformation is that a non-normalized propositional formula can be exponentially more succinct than its corresponding CNF. In Chapter 4,

| original                          | substitution                                            |

|-----------------------------------|---------------------------------------------------------|

| $\neg \neg \phi$                  | $\phi$                                                  |

| $\neg(\phi \lor \psi)$            | $\neg \phi \land \neg \psi$                             |

| $\neg(\phi \land \psi)$           | $\neg\phi \vee \neg\psi$                                |

| $\phi \Rightarrow \psi$           | $\neg\phi\lor\psi$                                      |

| $\phi \Leftrightarrow \psi$       | $(\phi \Rightarrow \psi) \land (\psi \Rightarrow \phi)$ |

| $(\phi_1 \land \phi_2) \lor \psi$ | $(\phi_1 \lor \psi) \land (\phi_2 \lor \psi)$           |

Table 2.1: Simple transformation to CNF.

more sophisticated translation strategies will be described which avoid this problem by introducing new variables for subformulas.

For many problems, a circuit is a more direct representation of the original problem. We have already determined that a Boolean circuit C has  $2^{|input(\mathcal{C})|}$  consistent truth assignments, therefore it only makes sense to determine the satisfiability of a constrained circuit. For constrained circuits, we can define the satisfiability problem in the following way.

**Definition 12.** For a constrained circuit  $(C, \tau)$ , the Boolean circuit satisfiability problem (CIRCUIT-SAT) is to decide whether  $(C, \tau)$  is satisfiable, i.e., whether there is a consistent extension of  $\tau$ .

A number of decision problems about propositional formulas can be cast into the form of a satisfiability problem.

**Remark.** For two propositional formulas  $\phi$  and  $\psi$  it holds that

- (i)  $\phi$  is valid **iff**  $\neg \phi$  is unsatisfiable.

- (ii)  $\phi \models \psi$  iff  $\neg(\phi \Rightarrow \psi)$  is unsatisfiable.

- (iii)  $\phi$  and  $\psi$  are equivalent iff  $\neg(\phi \Leftrightarrow \psi)$  is unsatisfiable.

Furthermore, most SAT-solvers do not simply return a binary answer to the satisfiability problem, but they also provide a model for satisfiable instances. The information encoded in this model can be used to gain more information about the problem. In SAT instances obtained from hardware or software verification problems, an interpretation can yield an error trace leading up to a problem state, in SAT-based planning, an interpretation can be transformed into a ready-made plan. A number of decision problems about propositional formulas can be cast into the form of a satisfiability problem.

For an illustration of how a given problem can be encoded into a propositional form, see the example provided in Figure 2.2.

### 2.3 Basic Algorithms for the SAT-Problem

Developing solvers that perform reasonably well on interesting classes of instances (such as encodings of real-world problems) is a hard problem, both from a theoretical as well

| 1 | 3 |   |

|---|---|---|

|   | 4 |   |

|   |   | 2 |

|   |   |   |

Sudoku is a simple puzzle that can be easily transformed into a SAT-instance. In the small example to the left it consists of a  $2 \times 2$  arrangement of  $2 \times 2$  boxes. Each small  $2 \times 2$  box should be filled with the numbers from 1 to 4, likewise, each row and column should contain each of the numbers. In our encoding, we use variables of the form  $n_{x,y}$ , where  $I(n_{x,y}) = 1$  means that the number n is at the location x, y. In order to represent the puzzle rules we need to define some propositional constraints.

First of all, an auxiliary construction is needed that builds from a set of propositional atoms S a propositional formula that is true iff exactly one of the atoms in S is true.

$$exactlyOne(S) = \bigvee_{q \in S} q \land \bigwedge_{q \in S} (\bigwedge_{r \in S \setminus \{q\}} \neg q \lor \neg r)$$

We can now define the actual constraints of the Sudoku domain.

$$\begin{aligned} uniqueAtLoc &= \bigwedge_{(x,y)\in\{1,2,3,4\}^2} exactlyOne(\{1_{x,y}, 2_{x,y}, 3_{x,y}, 4_{x,y}\}) \\ uniqueInRow(n,y) &= exactlyOne(\{n_{1,y}, n_{2,y}, n_{3,y}, n_{4,y}\}) \\ uniqueInCol(n,x) &= exactlyOne(\{n_{x,1}, n_{x,2}, n_{x,3}, n_{x,4}\}) \\ uniqueInBox(n, b_x, b_y) &= exactlyOne(\{n_{2*b_x + \Delta_x, 2*b_y + \Delta_y} \mid (\Delta_x, \Delta_y) \in \{1,2\}^2\}) \end{aligned}$$

These constraints encode that each grid location contains exactly one number (uniqueAtLoc), and that each row, column, and  $2 \times 2$  box contain each number from one to four exactly once (uniqueInRow, uniqueInCol, uniqueInBox). Now we only need to set up the initial information set in the instance shown in the picture above,

*init* =

$$1_{1,1} \wedge 3_{2,1} \wedge 4_{2,2} \wedge 2_{4,3}$$

The resulting propositional formula is now,

$$\begin{split} \phi = uniqueAtLoc & \wedge & init \\ & \wedge & \bigwedge_{n \in \{1,2,3,4\}} \bigwedge_{(b_x,b_y) \in \{0,1\}^2} (uniqueInBox(n,b_x,b_y)) \\ & \wedge & \bigwedge_{n \in \{1,2,3,4\}} \bigwedge_{i \in \{1,2,3,4\}} (uniqueInRow(n,i) \wedge uniqueInCol(n,i)) \end{split}$$

After finding an interpretation that satisfies  $\phi$  we can simply extract a solution to the Sudoku instance by looking at the values of the variables of the form  $n_{x,y}$ . If there is no solution, a SAT-solver would report the instance to be unsatisfiable.

Figure 2.2: Example for SAT encoding.

as from an engineering point of view. A conceptually simple but inefficient algorithm to determine the satisfiability of a given formula  $\phi$ , would be to enumerate all possible interpretations I and check whether any of those I satisfies  $\phi$ . Although this algorithm shares with all other known SAT algorithms a worst-case exponential time-complexity, it is not competitive in the average case for instances occurring in practice. This enumeration procedure also makes the NP-membership of SAT intuitive: A non-deterministic Turing machine can "guess" an interpretation I and then check in polynomial time whether I satisfies  $\phi$ .

In the literature, most algorithms are based on propositional formulas given in CNF. These can be further divided into two main classes, stochastic algorithms and systematic algorithms. The former tend to view SAT as an optimization problem with the goal of maximizing the number of satisfied clauses and employ stochastic search strategies through the space of interpretations. If such strategies are not combined with systematic approaches, stochastic procedures are incomplete, that is, they may be able to find a satisfying interpretation for a formula, but they cannot show that a given instance is unsatisfiable.

An incomplete SAT solver can still be useful. In many verification applications, for example, a satisfying interpretation yields a trace leading up to an error state. In such a case, an incomplete solver can help to find bugs, but it can never prove that the given system is bug-free.

Systematic algorithms, on the other hand, typically build partial assignments in a systematic way until a satisfying assignment is found or until the space of interpretations has been fully explored. Most systematic algorithms are based on the Davis-Logemann-Loveland (DLL) [13] procedure, which in turn is based on the Davis-Putnam (DP) procedure [12]. Since the work presented in this thesis is closely related to the DLL procedure, both of them will be described in this section.

#### 2.3.1 The Davis-Putnam Algorithm

The DP algorithm was first presented in Davis and Putnam [12] and was originally used as part of a procedure for determining the validity of first order formulas (a problem that is, in general, undecidable). The DP algorithm works on a propositional formula in CNF and essentially combines the resolution rule with a search procedure.

**Definition 13.** Given two clauses  $c_1 = a_1 \vee \ldots \vee a_i \vee \ldots \vee a_l$  and  $c_2 = b_1 \vee \ldots \vee b_j \vee \ldots \vee b_k$ where  $a_i$  and  $b_j$  are literals of the same variable v in opposite phases, i.e.,  $a_i = \overline{b_j}$ , we call the clause

$c_3 = a_1 \vee \ldots \vee a_{i-1} \vee a_{i+1} \vee \ldots \vee a_l \vee b_1 \vee \ldots \vee b_{j-1} \vee b_{j+1} \vee \ldots \vee b_k$

the resolvent of  $c_1$  and  $c_2$  ( $c_1 \otimes_v c_2$ ). The variable v is the variable resolved upon.

The resolution rule states that given two clauses  $c_1$  and  $c_2$ , we can infer any of their resolvents  $c_3$ .

Given a SAT instance as a propositional formula in CNF, the original DP procedure iteratively modifies the formula by a sequence of satisfiability-preserving steps using the following rules.

- **Literal elimination** If a pair of one-literal clauses,  $c_1 = a$  and  $c_2 = \neg a$  exists where a is a propositional atom, conclude that the instance is unsatisfiable. If this is not the case, and a clause c = l exists where l is a literal, remove all clauses that contain l and remove  $\overline{l}$  from all remaining clauses. If the resulting formula is empty, conclude that the instance is satisfiable.

- Affirmative-negative rule For every variable that occurs only in one phase as a literal in the CNF, remove all clauses containing that literal.

- Elimination rule for propositional variables (originally referred to as "elimination rule for atomic formulas" in Davis and Putnam [12]). Choose a decision variable v and construct all possible resolvents upon that variable. Replace the original formula by a conjunction of the resolvents and all clauses in the original formula that do not contain a literal of v.

Upon closer analysis, it becomes clear that the first two rules are conceptually subsumed by the elimination rules if the critical variable v is chosen as decision variable. In order to show why this is true, consider the following scenario. If there is a one-literal clause c = l on decision variable v, all opposite phase occurrences are automatically eliminated. If a second one-literal  $c' = \overline{l}$  existed, its resolvent with c is the empty clause. The empty clause evaluates to false under any interpretation, therefore the instance is unsatisfiable.

A similar line of reasoning can be employed to show that the affirmative-negative rule is subsumed by the elimination rule. If a literal l only occurs in one phase, and its variable is chosen as elimination-rule variable, it has no possible resolvents. No additional clauses are therefore added to the formula in the elimination rule, but all clauses are removed that contain v. The result is then the elimination of all clauses that contained v.

By eliminating the first two rules, we can then gain a conceptually simpler variant of the DP algorithm.

**Init** Let  $\phi$  be the input formula.

- **Step 1** If  $\phi$  contains the empty clause, conclude unsatisfiability. If  $\phi$  is the empty conjunction, conclude satisfiability.

- **Step 2** Let v be a variable occurring in  $\phi$ . Let R be the set of all possible resolvent clauses upon the variable v from the clauses in  $\phi$ .

**Step 3** Let  $\phi'$  be the conjunction of R and all clauses in  $\phi$  that do not contain v.

**Step 4**  $\phi := \phi'$ . Goto step 1.

While this method terminates after a linear number of such high-level steps, the formula may grow exponentially in size during the resolution step. The algorithm is therefore of limited use for practically interesting problem instances.

#### 2.3.2 The Davis-Logemann-Loveland Algorithm

The DLL procedure (also referred to as DPLL) is a highly-efficient, backtracking-based algorithm for the SAT problem. It was presented in the 1962 paper by Davis, Logemann, and Loveland [13] as an improvement of the DP procedure, and it forms the basis of most competitive SAT solvers even today.

Originally, the DLL procedure was simply the DP procedure with the elimination rule replaced by the splitting rule due to the excessive worst-case memory consumption of the former.

**Splitting rule** Let v be variable occurring in  $\phi$ . Let A be the conjunction of those clauses that contain v in positive phase, let B be the conjunction of clauses that contain v in negative phase, and let R be the conjunction of clauses where v does not occur. Create  $A_{\setminus v}$  and  $B_{\setminus \neg v}$  by removing all occurrences of v and  $\neg v$  from the clauses in A and B respectively. Recursively determine the satisfiability of the formulas  $A_{\setminus v} \wedge R$  and  $B_{\setminus \neg v} \wedge R$ . Conclude satisfiability if either of the formulas is satisfiable, else conclude unsatisfiability.

The splitting rule transforms the earlier resolution-based method into a backtrack search procedure. We will therefore recharacterize the DLL procedure in a slightly different way which emphasizes the idea of search and is closer in spirit with modern implementations of DLL and its variants.

We can view the DLL algorithm as a depth-first-search (DFS) procedure in the space of partial assignments where, between each step of the search, the following two deduction rules are applied to prune parts of the search space.

- **Pure literal rule** If a literal occurs only in one phase in the set of unsatisfied clauses, it is set to be true in the current partial assignment.

- Unit rule Let I be the current partial interpretation. If, in an unsatisfied clause, all but one literals evaluate to false, then the remaining literal is set to be true in I.

The process is initialized with the empty partial assignment and incrementally expands this assignment through search and deduction. Under the current partial assignment, a clause is called *conflicting* if it evaluates to false, *satisfied* if it evaluates to true, *unit* if all but one of its literals evaluate to false, and *unresolved* otherwise.

If a conflict occurs, that is, if a clause is conflicting under the current partial assignment, then the DFS search backtracks to an earlier node in the search tree and continues the search from there.

The simplified structure of the DLL algorithm can be seen in Algorithm 2.1; an example run is shown in Figure 2.3. The *deduce* function exhaustively applies the two deduction rules presented above. In modern implementations, the pure literal rule is

| Algorithm 2.1: DLL                                                                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------|

| <b>input</b> : <i>I</i> - a partial interpretation, $\phi$ - a CNF formula<br><b>output</b> : Satisfiability of $\phi$                   |

| if deduce $(I, \phi) = Conflict$ then<br>$\  \                                 $                                                         |

| if allVarsAssigned( $I, \phi$ ) then<br>$\ \ \ $ return true;                                                                            |

| $v \leftarrow \texttt{chooseVar}(I, \phi);$                                                                                              |

| $\mathbf{return} \ \mathtt{DLL}(I \cup \{\mathtt{v} := \mathbf{T}\}, \phi) \lor \mathtt{DLL}(I \cup \{\mathtt{v} := \mathbf{F}\}, \phi)$ |

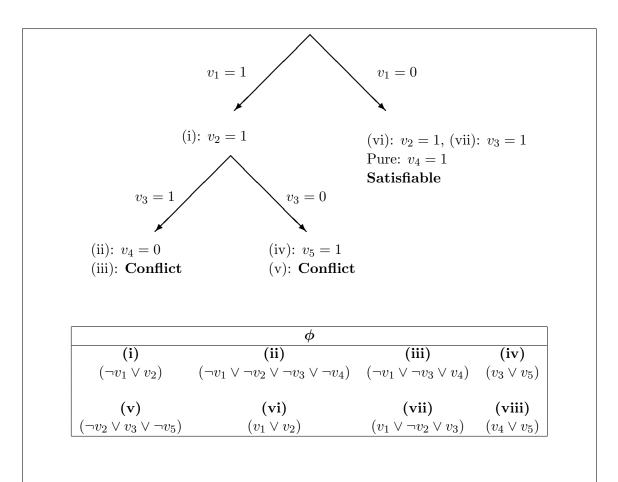

The above diagram depicts an example run of the DLL procedure on the input formula  $\phi$ , with clauses numbered (i) through (viii). The tree is expanded left-to-right, applications of the unit rule and conflicts are prefixed with the numeral of the relevant clause, applications of the pure-literal rule are prefixed with "pure".

Figure 2.3: Exemplary DLL run on formula  $\phi$ .

only used in preprocessing since the overhead costs necessary to detect the applicability of the rule outweigh the benefits of the additional deductions.

The DLL procedure is highly sensitive to the choice of decision variables. Usually, some kind of greedy heuristic is used that aims at maximizing the occurrence of possible unit-rule applications or conflicts. In most modern DLL-based solvers, heuristics are chosen which aim to produce conflicts as early as possible in order to avoid entering unnecessary regions of the search space.

### 2.4 Practical Applications of SAT-Solvers

Modern SAT solvers have reached a degree of efficiency where they are able to solve real-world instances with hundreds of thousands of variables. There is a multitude of possible applications, including applications in software and hardware verification, hardware testing, and logic-based planning.

In order to give some insight in how SAT solvers can be used to solve problems of practical interest, a small selection of them will be presented here.

#### 2.4.1 Bounded Model Checking

For purposes of CNF-SAT based verification, a given Boolean circuit can be transformed into a propositional formula. Such a formula is trivially satisfiable as long as the circuit is unconstrained, i.e., as long as there is no gate that is forced to assume a specified output value. A satisfiable assignment can easily be found by assigning random values to all inputs and propagating them across the circuit. If one wants to test certain properties about the given circuit, those properties must be encoded in propositional form and added to the formula as constraints.

As an example, imagine a circuit controlling the launch of a nuclear weapon. As a security measure, two keys need to be inserted into the launching mechanism and turned at the same time in order to fire the weapon, thus requiring at least two people to initiate a launch. Let C be a Boolean circuit model of the controlling circuit. In the circuit model, the fact that a key has been turned is represented by the primary inputs  $k_1$  and  $k_2$  for the first and second key respectively. An assignment  $k_1 := \mathbf{T}$  and  $k_2 := \mathbf{T}$  would therefore represent that both keys are currently turned, and that the weapon should thus be fired. This should also be the only assignment to  $k_1$  and  $k_2$  that should initiate the launch sequence, which is represented itself by the primary output assignment  $l := \mathbf{T}$ . We could therefore introduce a design specification  $(l \Rightarrow (k_1 \land k_2))$ .

In order to verify this specification, we could translate the behaviour of the circuit into a propositional formula  $\phi$  and check the formula  $\psi = \phi \Rightarrow (l \Rightarrow (k_1 \land k_2))$  for validity. We can do this by using a SAT solver on the formula  $\neg \psi$ . If the solver returns that the formula is satisfiable, there is an error in the design of our circuit C. In the model that is returned, a state is encoded where the launch sequence is initiated  $(l := \mathbf{T})$ but at least on of the keys is not turned  $(k_1 := \mathbf{F} \text{ or } k_2 := \mathbf{F})$ .

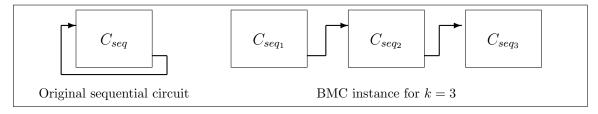

Figure 2.4: Instancing a sequential circuit for BMC.

Real problems in hardware or software verification do not come in the form of combinatorial circuits, but are usually sequential in nature. A sequential circuit cannot trivially be transformed into a propositional formula, but it is possible to construct a combinatorial circuit which simulates its behavior up to a fixed number of time-steps. The resulting circuit, together with certain properties that specify the expected behaviour can be modeled as a propositional formula and checked using a SAT solver. This technique is called *bounded model checking* (BMC) and was pioneered in Biere, Cimatti, Clarke, Fujita, and Zhu [7].

The main idea is fairly simple and will be briefly sketched here. Given a sequential circuit and a bound k, we first model the circuit as a Boolean circuit  $C_{seq}$  by removing all feedback loops. Then, k instances  $C_{seq_1}$  to  $C_{seq_k}$  of  $C_{seq}$  are created where in each, the gates are replaced by a fresh set of identical gates. Finally, for each instance, each primary output gate that feeds back into the circuit in the original sequential circuit is connected to the input gate of the next instance, e.g., the outputs of  $C_{seq_1}$  are connected to  $C_{seq_2}$ , etc. Figure 2.4 provides an example.

The resulting Boolean circuit is then translated into a propositional formula. Specifications given in some formal language such as temporal logic are translated into propositional form as well, and the conjunction of the specification and the circuit description is evaluated using a SAT solver.

By running multiple iterations of this process with increasing values of k, counterexamples to the specification with minimal length can be found. This iterative procedure is only complete if it is run until k exceeds a certain *completeness threshold* that depends on the BMC instance. If the minimal counterexample that is needed to produce the error is longer than the highest bound k that is tested, it is possible for errors to remain undetected.

#### 2.4.2 Automatic Test Pattern Generation

During the production of microchips, certain imprecisions in the production process can lead to faulty circuits. In order to ensure the correct functioning of a chip, it is necessary to apply test input patterns to the circuit and compare them with the expected outputs. Since exhaustively testing the circuit is usually intractable, a certain set of test patterns have to be selected. This selection process, if it is to ensure the correct functioning of the chip, is not trivial. Faulty outputs of gates in the circuit may be masked by other values under certain conditions, or a gate could never be accessed in a way that produces a faulty output.

The basic problem in automatic test pattern generation (ATPG) is finding test inputs which cause output values to diverge if a specified defect exists in the circuit.

In order to be able to detect a certain class of fault, a fault model is needed first, that is, a mathematical description of the fault. One of the most commonly used models is the stuck-at-fault model (SAFM). It assumes that a gate, instead of calculating the appropriate Boolean function, is stuck at a constant truth value. In the stuck-at-fault-model, the ATPG problem for a gate g is to find input patterns that cause the output values of a circuit to diverge from the original circuit's behavior if g's output is a constant true or false signal.

While many dedicated algorithms have been developed to solve this problem, encoding the problem as an instance of SAT has proven to be very efficient given the speed of modern solvers. In a 1996 paper, Stephan, Brayton, and Sangiovanni-Vincentelli [41] already show a SAT solver to be a very robust alternative to dedicated algorithms. Since then, SAT-solver performance has increased considerably.

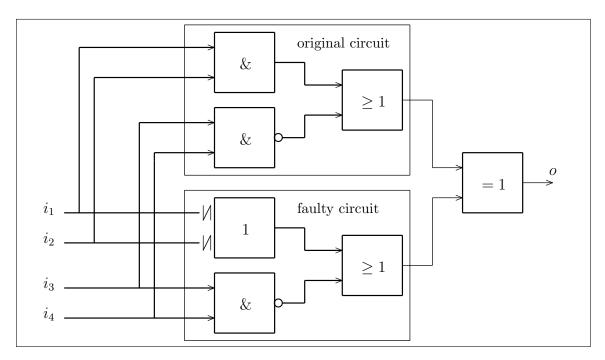

The basic idea for a SAT-based encoding is sketched in Figure 2.5. A circuit is constructed which encodes relevant parts of the original as well as the faulty circuit, both being connected to the same inputs. A checker is introduced, which compares the output of the two subcircuits and reports divergences. This circuit is encoded into a propositional formula, and a constraint is added that forces the checker to be true, i.e., the compound circuits' output to diverge. If a satisfying assignment is found for this circuit (which should be the case if the faulty gate is not redundant), the input values can be extracted from the satisfying interpretation and used as a test pattern.

Figure 2.5: Circuit construction for ATPG-to-SAT transformation. A stuck-at-true fault for an AND-gate is analyzed. The primary output o is true if  $i_1$  to  $i_4$  are set the values that make the output of the original and faulty circuit diverge.

# Chapter 3

# Improvements Over The Standard DLL Framework

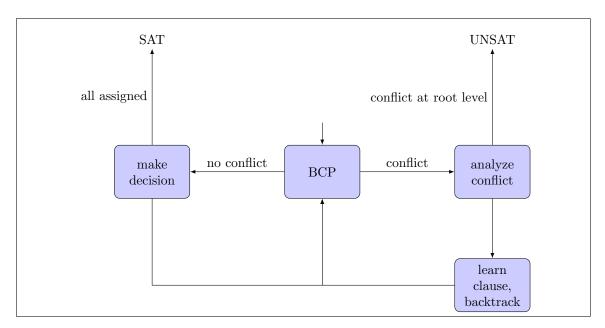

While the DLL procedure has proven to be a highly efficient framework for the development of SAT solvers, a naive implementation is unlikely to be competitive on any realistic set of benchmarks. The combination of non-chronological backtracking and learning with the DLL procedure (independently introduced in the solver Grasp [33] and in the work of Bayardo and Schrag [2]) in the mid-1990s increased the interest in the DLL procedure as a framework for SAT solvers considerably. Since then, numerous improvements and refinements have been proposed for the standard algorithm which increase its speed considerably. These can be grouped into two main categories.

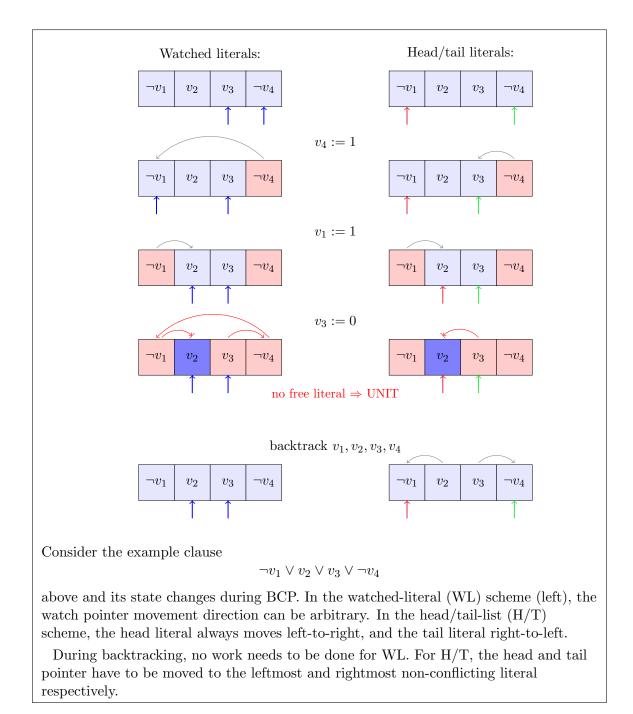

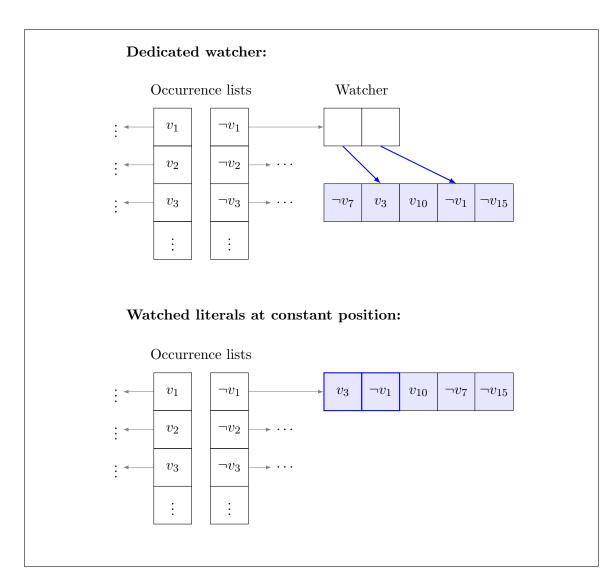

First, datastructures and implementation techniques have been proposed which, while not changing the high-level behaviour of the procedure, allow for considerable speed-ups. For SAT solvers, low-level efficiency is extremely important. In modern implementations, about 90% of the runtime is spent in *Boolean Constraint Propagation* (BCP), i.e., in the exhaustive application of the unit rule. Low-level improvements can therefore easily lead to big overall speed-ups. CNF is a structurally very simple format for propositional formulas and lends itself especially well to efficient implementation techniques.

Second, improvements have been made to the way the DLL procedure searches the space of partial assignments. These include the development of various heuristics which aim at finding good decision variables and the analysis of conflicts. The information gained from a conflict can be used to prune unnecessary parts of the search space and learn deduction shortcuts that can be applied if a similar region of the search space is reentered at a later time.

In this section, low-level as well as high-level improvements to the DLL procedure will be presented that have been shown to work well on practical problem instances.

### 3.1 The DLL Algorithm Revisited

A recursive version of the DLL algorithm was already presented in Chapter 2. In Algorithm 3.1, a basic iterative version of the DLL algorithm is shown. This formulation is closer to actual implementations, and will be used in order to fix some basic definitions and notation.

First, a check is performed whether a conflict occurs without making any decisions, and if that is the case, the algorithm returns the instance to be unsatisfiable. Otherwise, we enter the main loop of the procedure.

First, the decide function is called, which either makes a decision and returns true, or returns false if no more unassigned variables exist. In the latter case, the instance is satisfied and the algorithm stops. Otherwise, the decision assignment is propagated via BCP in the deduce function. If a conflict occurs, the procedure backtracks to the last level where the decision variable has not been tried out in both phases. If no such level exists, that is, if all branches have been explored and found to be conflicting, the algorithm returns the instance to be unsatisfiable. After backtracking, the solver enters an unexplored branch of the search tree by flipping the previous decision assignment on the backtracking level (flipLastDecision).

```

Algorithm 3.1: Iterative DLL

```

```

input : A CNF formula \phi

output: Satisfiability of \phi

I \leftarrow \emptyset;

dLevel \leftarrow 0:

if deduce (I, \phi) = Conflict then

\lfloor return unsat;

while true do

// Check if all variables are assigned, else make decision assignment

if \neg decide(I, \phi) then

| return sat;

dLevel \leftarrow dLevel + 1;

while deduce (I, \phi) = Conflict do

repeat

undoAssignments(I,dLevel);

dLevel \leftarrow dLevel - 1;

until dLevel > 0 \land \texttt{triedBothPhases(dLevel)};

if dLevel = \theta then

return unsat;

else

dLevel \leftarrow dLevel + 1;

flipLastDecision(dLevel);

```

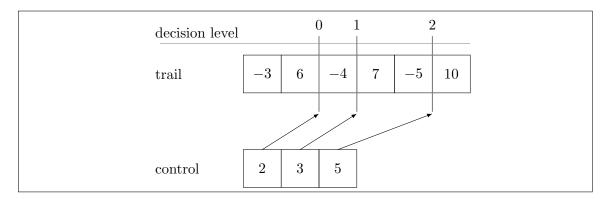

The variable dLevel denotes the current decision level of the solver. The decision

level equals the number of decisions made on the current search branch. The decision level of a variable v, dLevel(v), is the decision level of the solver when the assignment was made. The assignment of a variable v to a value  $x \in \{\mathbf{T}, \mathbf{F}\}$  in the current partial interpretation will be denoted by v := x. When necessary, this notation is extended to v := x @d where d = dLevel(v).

Note, that only the unit-rule is used in the deduce step. The pure-literal rule is usually too expensive to be applied in every step of the search process, and its elimination does not affect completeness.

## 3.2 Clause Learning and Non-Chronological Backtracking

In the mid-nineties, two improvements, *non-chronological backtracking* and *clause learn-ing* were first used in SAT solving [33; 2]. In clause learning, new clauses are added to the clause database when a conflict is encountered. Such new clauses serve as deduction shortcuts if a similar region of the search space is entered later on. Non-chronological backtracking uses conflict analysis to identify possibilities for jumping back past unexplored branches, if those branches of the search tree are sure to lead to conflicts.

The combination of these techniques increased solving efficiency considerably. The general framework of the DLL algorithm with clause learning and non-chronological backtracking has been the foundation for the most efficient solvers for industrial instances to date.

#### 3.2.1 Clause Learning

The original DLL procedure is simply a systematic search process through the space of partial assignments. Assignments are iteratively enlarged until either a satisfying assignment is found or a conflict is encountered, which causes the algorithm to backtrack. Many of the conflicts that occur during the search procedure may have the same or similar causes. Consider as an example the following CNF formula  $\phi$ ,

$$\phi = (x_1 \lor x_2 \lor x_3) \land (x_1 \lor x_2 \lor \neg x_3) \land (\ldots \lor \ldots \lor \ldots) \land \ldots \land (\ldots \lor \ldots \lor \ldots).$$

If  $x_1$  and  $x_2$  are both false at some point during the search, a conflict will occur since we can deduce that  $x_3 = \mathbf{T}$  and that  $x_3 = \mathbf{F}$  using the unit rule. This conflict may occur exponentially often in the number of variables of  $\phi$ . To a human, it would become clear soon that  $x_1$  must be true whenever  $x_2$  is false, and vice versa. This information can be used to avoid entering regions of the search space that are sure to lead to conflicts.

It is surprisingly easy to add this technique to a DLL framework. In our case, we can simply use the propositional constraint  $\neg(\neg x_1 \land \neg x_2)$  to encode our knowledge that not both  $x_1$  or  $x_2$  may be false. Pushing the negation down to the literals with De Morgan's rule leaves us with the clause  $(x_1 \lor x_2)$  which subsumes both of the original clauses and can be added to our original formula. Note, that this would also be the resolvent of the two clauses. Whenever one of the two variables now becomes false, the unit rule can be immediately used to determine that the other variable must be true. We therefore save a decision and the additional inspection of the search tree that it would entail. Such a clause is called a *learned clause* or a *conflict clause* (a *conflicting clause*, in contrast, is a clause that evaluates to false under the current partial interpretation). The learned clause is redundant, the new formula with the added learned clause is therefore logically equivalent to the original one. One can think of the learned clause as a deduction shortcut since the information it encodes is already contained in the original CNF formula.

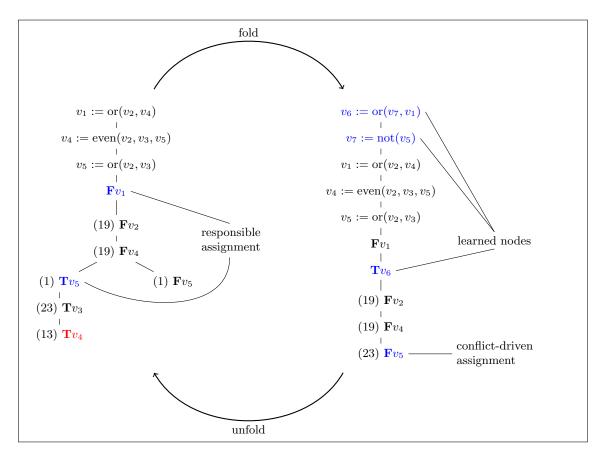

The main idea behind conflict analysis and clause learning is to generalize the above idea. Information is extracted from conflicts which is then used to avoid entering similar regions of the search space later on. This is done by tracing back a conflict to a *responsible variable assignment*.

Given a CNF formula  $\phi$ , We call an assignment A responsible for a conflict, if A is sufficient for producing the conflict via BCP. More formally, an assignment A is responsible for an extension A' of A iff A' can be produced by repeatedly extending A using the unit rule. We call A responsible for a conflict, if it is responsible for a total assignment that is not a model.

After identifying such a responsible assignment, we can add a clause which prevents any extension of that assignment from occurring again. Intuitively, we try to find and encode the reasons for a given conflict in order to avoid running into the same conflict again later on.

In general, such an assignment can be found by repeatedly resolving the conflicting clause with those clauses that led up to the conflict by inducing assignments in BCP. Instead of using such a resolution-based characterization, we will use the notion of an *implication graph*.

**Definition 14.** At a given step of the DLL procedure on CNF formula  $\phi$ , the implication graph is a directed acyclic graph  $(\mathcal{A}, E)$  where

- A = A' ∪ □ and A' is the set of all possible variable assignments, i.e., A' = { (v := X) | v ∈ vars(φ), X ∈ {T, F} } with vars(φ) being the set of Boolean variables occurring in φ. The box □ is a special conflict node.

- There is an edge  $(a_k, a_l) \in E$  iff

- $-a_l$  was implied in the current DLL search branch during BCP by a clause c which contains the literal that is made to evaluate to false by  $a_k$  or

- $-a_l = \Box$  and  $a_k$  makes a literal in the conflicting clause evaluate to false.

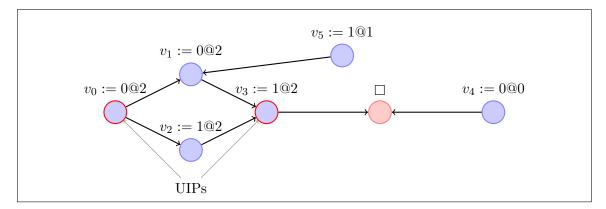

When a conflict occurs, we can traverse the implication graph  $(\mathcal{A}, E)$  backwards from the conflict node in order to identify a responsible assignments. This can be done by choosing a set of vertices  $S \subseteq V$ , so that each path on the implication graph from a decision to the current conflict passes through at least one node in S. The set of predecessors of the conflict node, for example, constitutes a trivial responsible assignment for the conflict. By replacing nodes with their predecessors (if such predecessors exist), we

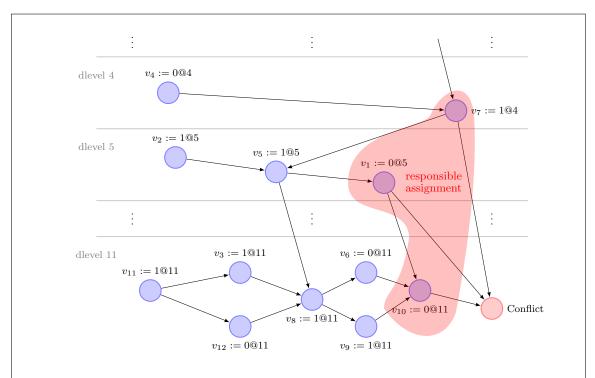

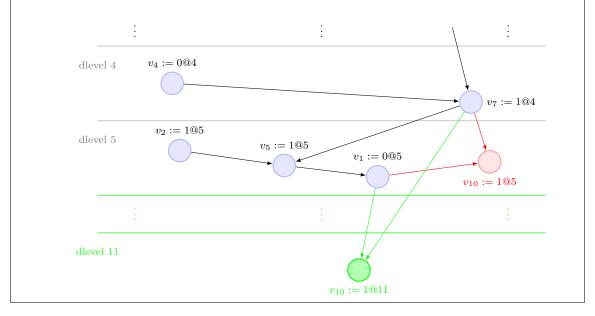

Above, an example of an implication graph at a conflict is shown. The chosen responsible assignment is indicated by the red area, the resulting conflict clause is  $c_{\text{confl}} = \neg v_7 \lor v_1 \lor v_{10}$ .

Newer implementations of conflict-driven backtracking (red) differ slightly from Grasp's original backtracking strategy [33] (green). Grasp backtracks to the highest decision level, newer solvers to the second-highest level.

Figure 3.1: Example for learning, non-chronological backtracking, and conflict-driven assignments.

can generate other responsible assignments. This "replacement" is actually a resolution step, as was briefly described before, the variable resolved upon being the variable that was assigned a value due to BCP. For an example of a responsible assignment after a conflict, consider Figure 3.1.

We can then create a clause which acts as a constraint, ensuring that the same set of assignments will not occur again. For the set of responsible assignments S, the added conflict clause  $c_S$  contains exactly those literals which are contradicted by the assignments in S, e.g., for  $S = \{x_1 := \top, x_2 := \bot, x_3 = \top\}$  we would have  $c_S =$  $\neg x_1 \lor x_2 \lor \neg x_3$ . The next time a similar region of the search space is encountered, the added clause may act as an implication shortcut which may instantly force a variable assignment via BCP, where otherwise, the solver would have to resort to decisions to determine the value of the variable.

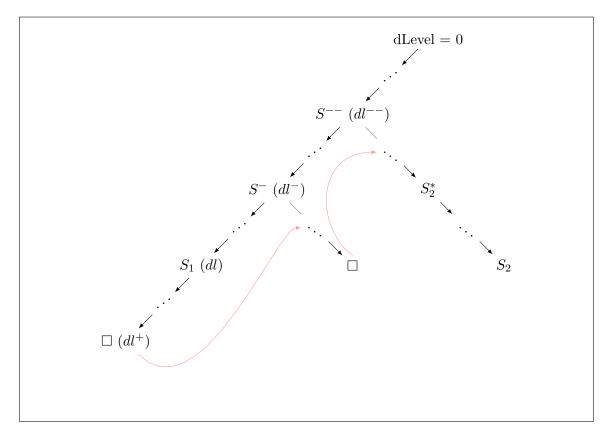

#### 3.2.2 Non-Chronological Backtracking

After a conflict has been identified, traditional implementations of the DLL procedure would backtrack chronologically, i.e., they would reset the solver to the highest decision level where both values of a decision variable have not been tried out. The solver would then proceed the solving process by assigning to this variable the so far untried value. This technique is called chronological backtracking.

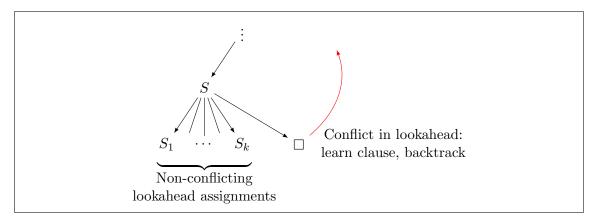

In non-chronological backtracking (also referred to as *conflict directed backjumping*), a solver may backtrack further than that, essentially leaving a number of branches unexplored. The main idea is that in backtracking, a SAT solver can skip over all unexplored branches which are sure not to lead to a satisfiable assignment. The identification of the backtracking level relies on the implication graph described above and is closely connected with the idea of learned clauses.

Non-chronological backtracking was not invented in SAT solving, but is a well studied technique originating in the area of constraint satisfaction problems under the name of "dependency directed backtracking" [40].

When a conflict is encountered, a clause is learned by analyzing the conflict and identifying a responsible assignment S from the implication graph. From this responsible assignment, we can determine the maximal decision level associated with any individual assignment in S

$$d_{\max} = \max_{(v:=X)\in S} \operatorname{dLevel}(v).$$

Since the learned clause is added to the instance, resulting in a logically equivalent instance, the solver state will remain conflicting until at least one of the assignments in S is undone. Even if the learned clause is not added to the clause database, the solver is guaranteed to encounter only conflicts if we backtrack to any decision level  $d \ge d_{\max}$  since the learned clause just provides a shortcut to an exploration of a certain part of the search space in the original instance. The unexplored branches from the current level up to the start of  $d_{\max}$  can safely be skipped.

Each of the skipped branches could theoretically unfold to a partial search tree that is exponential in the size of the remaining variables. Non-chronological backtracking can result in considerable performance improvements because it prevents the solver from entering or staying in such uninteresting regions of the search space.

We can also think of non-chronological backtracking as a way of recovering the solver from the negative consequences of bad decision orderings. In a good variable ordering, conflicts are produced as soon as possible, i.e., conflicting decisions are grouped close together. In the case of a bad ordering in the traditional DLL procedure, the variable assignments for a given conflict may occur on widely separated decision levels, which may lead to an exponential increase in runtime compared to a good ordering. Nonchronological backtracking can help to identify this wide level-span between conflicting variables and jump back to the earlier levels sooner.

#### 3.2.3 DLL with Clause Learning and Non-Chronological Backtracking